体系结构复习3

第3章 单周期MIPS处理器的设计

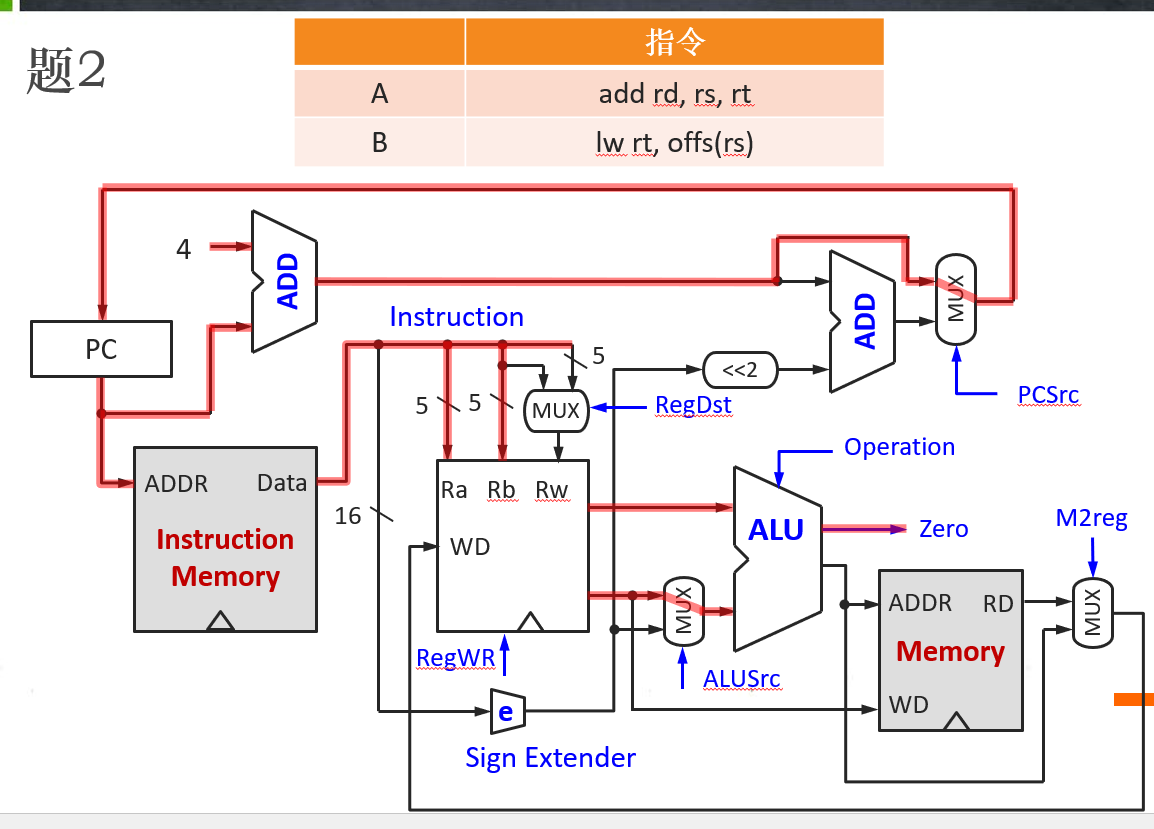

1.add, sub, addi, subi, lw, sw, beq, j 每条指令在单周期处理器中的执行逻辑

MIPS单周期处理器中各指令的执行逻辑

以下是 add、sub、addi、subi、lw、sw、beq 和 j 指令在单周期处理器中的执行逻辑,包括各个阶段和数据通路的工作流程。

1. R型指令:add 和 sub

R型指令用于寄存器之间的算术逻辑操作。

格式:

示例:

add rd, rs, rt:sub rd, rs, rt:

执行逻辑

取指(Instruction Fetch):

从指令存储器中取出指令,PC更新为 。译码(Instruction Decode):

读取指令中的寄存器地址字段:rs、rt和rd,从寄存器堆中读取rs和rt的值。执行(Execute):

- ALU 根据指令功能码(

funct字段)执行加法(add)或减法(sub)。 - 控制信号

ALUOp决定 ALU 执行加法或减法操作。

- ALU 根据指令功能码(

写回(Write Back):

将 ALU 的结果写回寄存器rd。

2. I型指令:addi 和 subi

I型指令用于立即数运算。

格式:

示例:

addi rt, rs, imm:subi rt, rs, imm:

执行逻辑

取指(Instruction Fetch):

从指令存储器中取出指令,PC更新为 。译码(Instruction Decode):

读取寄存器rs的值,同时将立即数imm进行符号扩展(16位扩展到32位)。执行(Execute):

ALU 执行加法或减法操作:- 操作数:寄存器

rs和扩展后的imm。

- 操作数:寄存器

写回(Write Back):

将结果写回寄存器rt。

3. 数据传输指令:lw 和 sw

lw(加载字) 和 sw(存储字) 用于数据传输。

- 格式:

执行逻辑

- lw rt, offset(rs):从存储器读取数据到寄存器

rt。 - sw rt, offset(rs):将寄存器

rt的数据存入存储器。

取指(Instruction Fetch):

从指令存储器取出指令,PC更新为 。译码(Instruction Decode):

读取基址寄存器rs的值,并将偏移量offset进行符号扩展。地址计算(Execute):

使用 ALU 计算目标地址:内存访问(Memory Access):

- lw:从存储器中读取数据,存入寄存器

rt。 - sw:将寄存器

rt的数据写入目标地址。

- lw:从存储器中读取数据,存入寄存器

写回(Write Back)(仅

lw):

将从存储器加载的数据写回寄存器rt。

4. 分支指令:beq

beq 指令用于条件分支。

格式:

示例:

beq rs, rt, offset- 如果 ,跳转到目标地址:

执行逻辑

取指(Instruction Fetch):

取出指令,PC 更新为 。译码(Instruction Decode):

读取寄存器rs和rt的值,并符号扩展偏移量offset。比较(Execute):

ALU 比较rs和rt的值是否相等。分支判断:

- 若 ,更新 PC:

- 否则继续执行下一条指令。

5. 跳转指令:j

j 指令用于无条件跳转。

格式:

示例:

j address- 跳转到目标地址:

执行逻辑

取指(Instruction Fetch):

取出指令,PC更新为 。目标地址计算(Execute):

拼接 PC 的高 4 位和指令的 26 位目标地址,得到跳转地址。PC更新:

将计算得到的目标地址写入 PC。

总结

| 指令 | 操作 | 执行过程 |

|---|---|---|

add |

取指 → 译码 → ALU运算 → 写回 | |

sub |

取指 → 译码 → ALU运算 → 写回 | |

addi |

取指 → 译码 → 符号扩展 → ALU运算 → 写回 | |

subi |

取指 → 译码 → 符号扩展 → ALU运算 → 写回 | |

lw |

取指 → 译码 → 地址计算 → 内存读取 → 写回 | |

sw |

取指 → 译码 → 地址计算 → 内存写入 | |

beq |

若 则分支跳转 | 取指 → 译码 → 比较 → 更新PC |

j |

无条件跳转到目标地址 | 取指 → 目标地址计算 → 更新PC |

2.上述指令的指令编码、代码、功能以及在单周期中的数据通路,条件分支指令的地址计算、单周期各功能部件的控制信号值判断

MIPS单周期处理器:指令编码、功能、数据通路与控制信号分析

以下是 add、sub、addi、subi、lw、sw、beq 和 j 指令的指令编码、代码功能、单周期中的数据通路以及控制信号的详细解析,包括条件分支指令的地址计算。

1. R型指令:add 和 sub

指令编码

- 格式:

- 示例编码:

add $t0, $t1, $t2sub $t0, $t1, $t2

功能

add:寄存器加法,结果存储到rdsub:寄存器减法,结果存储到rd

数据通路

- 寄存器堆:

- 读取

rs和rt两个寄存器的值。

- 读取

- ALU:

add或sub操作,根据 funct 字段判断具体操作。

- 写回:

- 将结果写回寄存器

rd。

- 将结果写回寄存器

控制信号

| 控制信号 | 值 | 功能 |

|---|---|---|

RegDst |

1 | 写回寄存器目的地址为 rd |

RegWrite |

1 | 使能寄存器写回 |

ALUSrc |

0 | ALU 第二个操作数来自寄存器 |

ALUOp |

10 | ALU 控制信号,R型指令判断功能码 |

2. I型指令:addi 和 subi

指令编码

- 格式:

- 示例编码:

addi $t0, $t1, 5

功能

addi:寄存器与立即数加法,结果存储到rt

数据通路

- 寄存器堆:

- 读取

rs的值。

- 读取

- 立即数扩展:

- 将 16 位

immediate进行符号扩展为 32 位。

- 将 16 位

- ALU:

- 执行加法操作:

rs + imm。

- 执行加法操作:

- 写回:

- 将结果写回寄存器

rt。

- 将结果写回寄存器

控制信号

| 控制信号 | 值 | 功能 |

|---|---|---|

RegDst |

0 | 写回寄存器目的地址为 rt |

RegWrite |

1 | 使能寄存器写回 |

ALUSrc |

1 | ALU 第二个操作数来自立即数 |

ALUOp |

00 | ALU 控制信号为加法操作 |

3. 数据传输指令:lw 和 sw

指令编码

- 格式:

- 示例编码:

lw $t0, 4($t1)

功能

- lw:加载字到寄存器

- sw:存储寄存器值到内存

数据通路

- 寄存器堆:

- 读取基址寄存器

rs。

- 读取基址寄存器

- 立即数扩展:

- 偏移量

offset符号扩展为 32 位。

- 偏移量

- ALU:

- 计算内存地址:

rs + offset。

- 计算内存地址:

- 数据存储器:

lw:从内存中读取数据写入rt。sw:将rt的数据写入内存。

控制信号

| 控制信号 | lw 值 | sw 值 | 功能 |

|---|---|---|---|

MemRead |

1 | 0 | 使能内存读取 |

MemWrite |

0 | 1 | 使能内存写入 |

ALUSrc |

1 | 1 | ALU 第二个操作数为偏移量 |

RegWrite |

1 | 0 | lw 需写回寄存器 |

4. 分支指令:beq

指令编码

- 格式:

功能

beq:若两个寄存器相等,则跳转

数据通路

- 寄存器堆:

- 读取

rs和rt的值。

- 读取

- ALU:

- 比较

rs和rt,生成Zero信号。

- 比较

- PC更新:

- 若

Zero = 1,跳转地址:PC + 4 + (offset << 2)。

- 若

控制信号

| 控制信号 | 值 | 功能 |

|---|---|---|

Branch |

1 | 使能分支跳转 |

ALUOp |

01 | ALU 控制信号进行比较操作 |

5. 跳转指令:j

指令编码

- 格式:

功能

j:无条件跳转

数据通路

- 目标地址计算:

- 将指令中的 26 位地址左移2位,与 PC 高 4 位拼接。

- PC更新:

- 将计算得到的目标地址写入 PC。

控制信号

| 控制信号 | 值 | 功能 |

|---|---|---|

Jump |

1 | 使能无条件跳转 |

总结表格

| 指令 | 功能 | 关键控制信号 |

|---|---|---|

add |

RegDst=1, ALUSrc=0, RegWrite=1 |

|

sub |

RegDst=1, ALUSrc=0, RegWrite=1 |

|

addi |

RegDst=0, ALUSrc=1, RegWrite=1 |

|

lw |

MemRead=1, ALUSrc=1, RegWrite=1 |

|

sw |

MemWrite=1, ALUSrc=1, RegWrite=0 |

|

beq |

若 则分支跳转 | Branch=1, ALUSrc=0, ALUOp=01 |

j |

无条件跳转到目标地址 | Jump=1 |

以下是您需要的 add、sub、addi、subi、lw、sw、beq 和 j 指令的操作码及相关信息总结:

1. R型指令

R型指令的操作码固定为 000000,具体功能由 功能码(funct) 决定。

| 指令 | 功能 | 操作码(op) | 功能码(funct) |

|---|---|---|---|

add |

加法 | 000000 |

100000 |

sub |

减法 | 000000 |

100010 |

2. I型指令

I型指令的功能由操作码(op)直接决定。

| 指令 | 功能 | 操作码(op) |

|---|---|---|

addi |

加法(立即数) | 001000 |

subi |

减法(立即数) | (无标准指令,在MIPS中未定义) |

lw |

加载字 | 100011 |

sw |

存储字 | 101011 |

beq |

分支(相等跳转) | 000100 |

3. J型指令

J型指令的功能由操作码(op)直接决定。

| 指令 | 功能 | 操作码(op) |

|---|---|---|

j |

无条件跳转 | 000010 |

4. 总结表格

| 指令类型 | 指令 | 功能 | 操作码(op) | 功能码(funct,R型指令专用) |

|---|---|---|---|---|

| R型 | add |

加法 | 000000 |

100000 |

sub |

减法 | 000000 |

100010 |

|

| I型 | addi |

加法(立即数) | 001000 |

- |

subi |

减法(立即数,未定义) | N/A | - | |

lw |

加载字 | 100011 |

- | |

sw |

存储字 | 101011 |

- | |

beq |

分支(相等跳转) | 000100 |

- | |

| J型 | j |

无条件跳转 | 000010 |

- |

注意

subi指令:在标准 MIPS 指令集中,subi并未被定义,可以通过addi使用负数立即数来替代。例如:R型指令 使用

funct字段指定具体功能,其op始终为000000。I型和J型指令 直接通过

op字段来确定功能,无需funct字段。

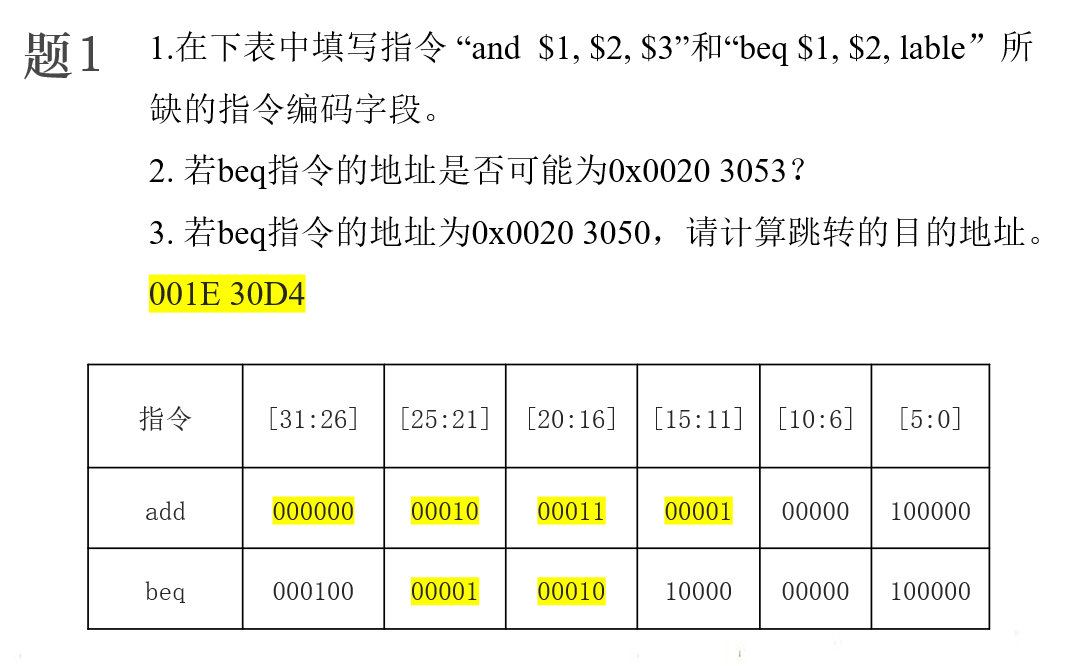

例题

题目分析与解答

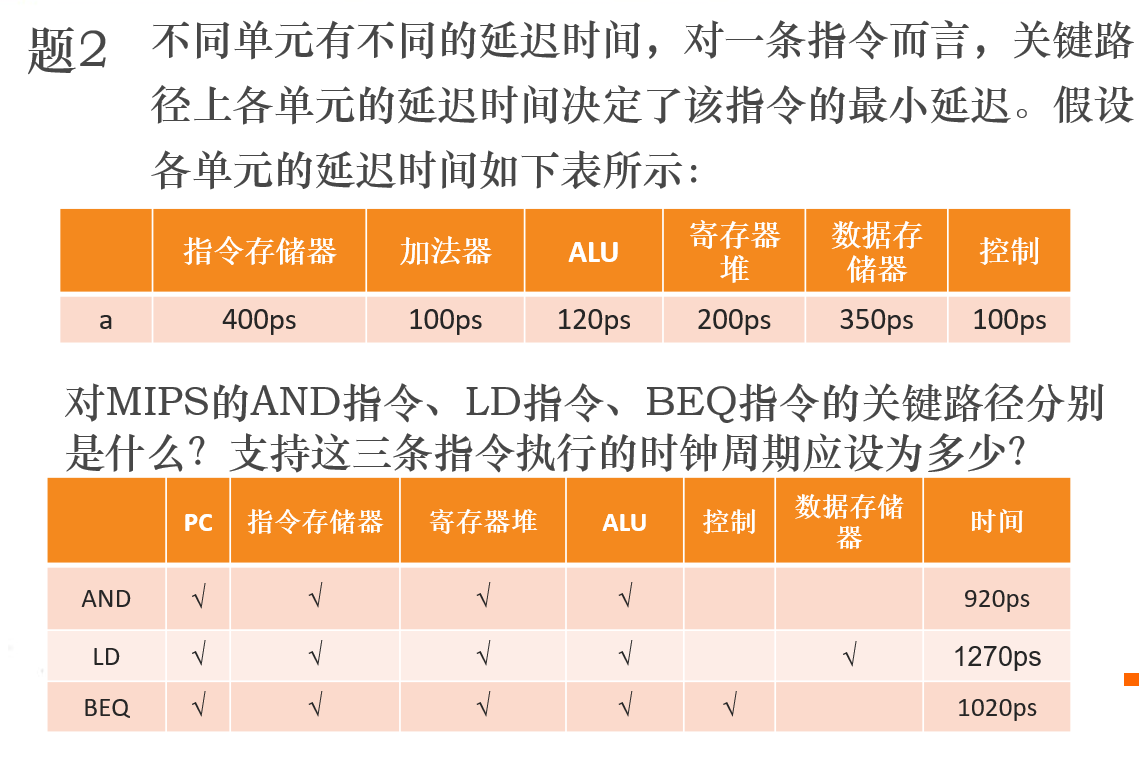

题目中要求我们分析 MIPS 指令(AND、LD 和 BEQ)在执行过程中涉及的关键路径,并根据每个模块的延迟时间计算总延迟。

1. 问题分析

- 每条指令的执行会经过不同的数据路径,关键路径是指令执行时耗时最长的路径。

已知每个模块的延迟时间:

- 指令存储器:400ps

- 加法器:100ps

- ALU:120ps

- 寄存器堆:200ps

- 数据存储器:350ps

- 控制单元:100ps

需要计算的三种指令:

- AND 指令(R型指令):涉及寄存器堆和 ALU。

- LD 指令(加载指令):涉及寄存器堆、ALU 和数据存储器。

- BEQ 指令(分支指令):涉及寄存器堆、ALU 和控制单元。

2. 关键路径分析

(1) AND 指令(R型指令)

- 路径:

PC -> 指令存储器 -> 寄存器堆 -> ALU -> 寄存器堆- 指令存储器:400ps

- 寄存器堆(读取):200ps

- ALU:120ps

- 寄存器堆(写入):不计入关键路径,因为写操作发生在时钟边沿。

- 总延迟时间:

(2) LD 指令(I型指令)

- 路径:

PC -> 指令存储器 -> 寄存器堆 -> ALU -> 数据存储器 -> 寄存器堆- 指令存储器:400ps

- 寄存器堆(读取):200ps

- ALU:120ps

- 数据存储器:350ps

- 寄存器堆(写入):不计入关键路径。

- 总延迟时间:

(3) BEQ 指令(分支指令)

- 路径:

PC -> 指令存储器 -> 寄存器堆 -> ALU -> 控制单元- 指令存储器:400ps

- 寄存器堆(读取):200ps

- ALU:120ps

- 控制单元:100ps

- 总延迟时间:

3. 总结表格

| 指令类型 | 涉及模块 | 延迟时间(ps) |

|---|---|---|

| AND | 指令存储器 -> 寄存器堆 -> ALU | 920 |

| LD | 指令存储器 -> 寄存器堆 -> ALU -> 数据存储器 | 1070 |

| BEQ | 指令存储器 -> 寄存器堆 -> ALU -> 控制单元 | 1020 |

4. 结果

- AND 指令关键路径延迟时间:920ps

- LD 指令关键路径延迟时间:1070ps

- BEQ 指令关键路径延迟时间:1020ps